MTE325

Course that Shaheer sent me notes for.

Concepts

Notes

Chapter 3

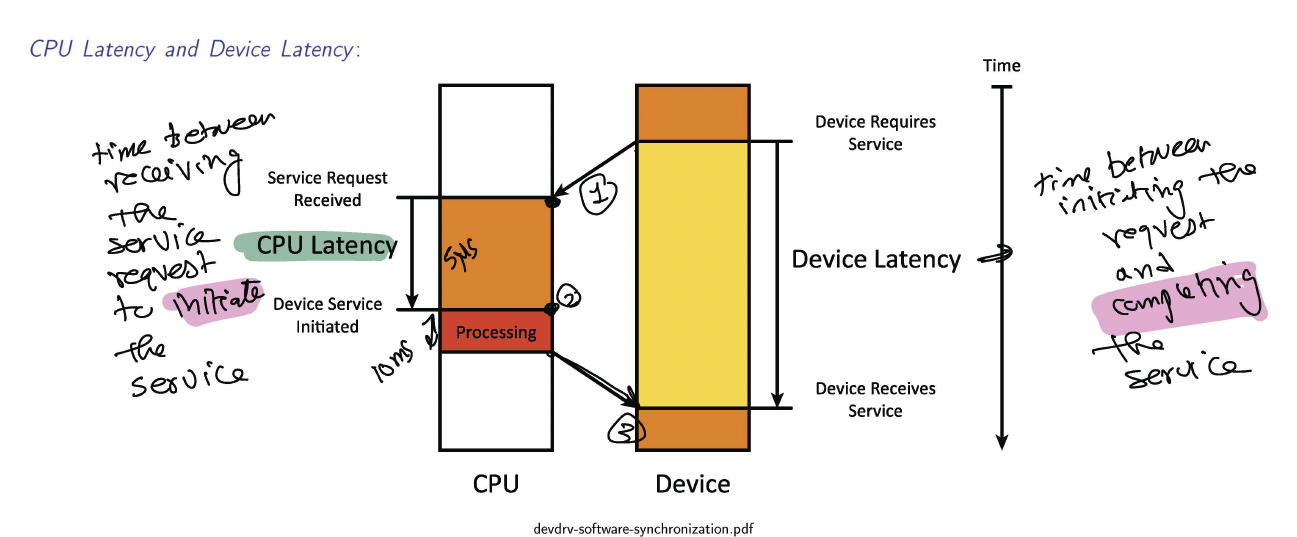

CPU Latency and Device Latency:

- CPU Latency: the time between the receipt of a service request and the initiation of service

- Device Latency: time between initiating the request and completing the request

Some terminology

- Real-time system: A system that guarantees a worst-case latency for critical events.

- Latency: the delay between the arrival of the request and the completion of service.

- Throughput: a measure of how many items can be processed per unit of time

Device Driver

A device driver is the software associated with a particular device. It includes

- Data Structures

- Initialization Functions

- I/O functions

- Interrupt Service Routines

Synchronization Mechanisms

CPU-Oriented (Device waits for CPU to initiate synchronization) mechanisms:

- Blind Cycle: Software waits for some amount of time and then acts on the data whether or not the device is ready.

- Occasional Polling: Device status is checked at the convenience of the designer.

- Periodic Polling: Device status is checked after a pre-determined amount of time and this repeats until the device is done. This is usually implemented with a timer interrupt.

Device-Oriented (Device demands immediate service to reduce device latency) 4. Tight Polling Loop (or Busy Waiting): Software continuously checks the I/0 status, waiting for the device to be done. Although this is often implemented as a very tight loop (i.e., continuously testing one status register and looping until the device is ready), it could be implemented as a sequence of tests (i.e., continuously testing a set of status registers and looping until a device in the set is ready). 5. Interrupt Handling (lowest latency): Device generates a hardware interrupt to request service immediately

Interrupt Synchronization

- A device notifies the CPU of an interrupt request

- CPU completes execution of the current instruction

- Execution of the main program is suspended

- Interrupts are disabled (processor specific)

- Some internal registers are saved (including the program counter)

- Device may be acknowledged

- Interrupt service routine is selected

- Interrupt service routine is executed (more on this later)

- Registers are restored, if required, including the program counter

- Interrupts are enabled (processor specific)

- Execution of the main program resumes

Chapter 4

Synchronization refers to the interaction required to make two entities interact.

- Active Synchronization: One of the entities is capable of forcing a change in the operational characteristics of the other. For example, setting an interrupt signal can force the processor to execute the interrupt service routine

- Passive Synchronization: One of the communicating entities signals a request for service, however the entity receiving the request is not forced to respond.

Synchronization must be considered at several levels. Consider the transfer of data from the following levels

- How is the data creation controlled (if it is controlled). How is it started? How is it stopped? Is this done by the producer or the consumer?

- Once the producer has the data, how does the producer notify the consumer that it is ready for the data to be consumed? Or, alternatively how does the consumer request the data 7

- Once the producer has the data and the consumer is ready for the Data, how it the timing (synchronization) of the transfer handled?

Chapter 5

I think this is where the fundamental knowledge is.

Types of Registers:

- General Purpose Registers: Provide internal storage for intermediate results

- Special Purpose Registers

- Program Counter

- Instruction Register

- Program Status Register

- Stack Pointer

- Memory Address Register

- Memory Data Register

Ahh, I actually learned all this on CS241E< I didn’t learn about IR, MAR and MDR because they are not directly accessible to a programmer.