Clock

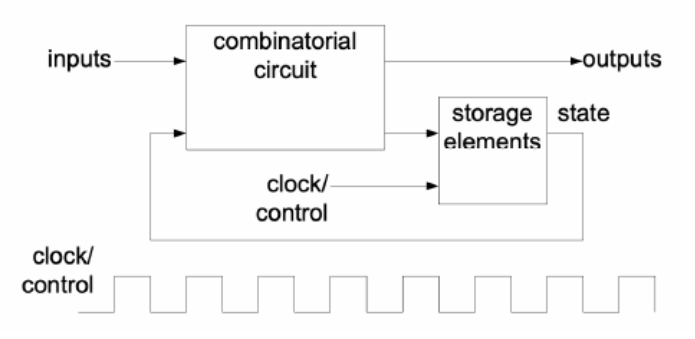

Clock signals are particularly important to understand for designing synchronous Sequential Circuits (aka clocked sequential circuits).

A clock signal is used to control the behavior of a circuit at discrete instances in time

- by controlling/determining how and when memory elements can change their outputs.

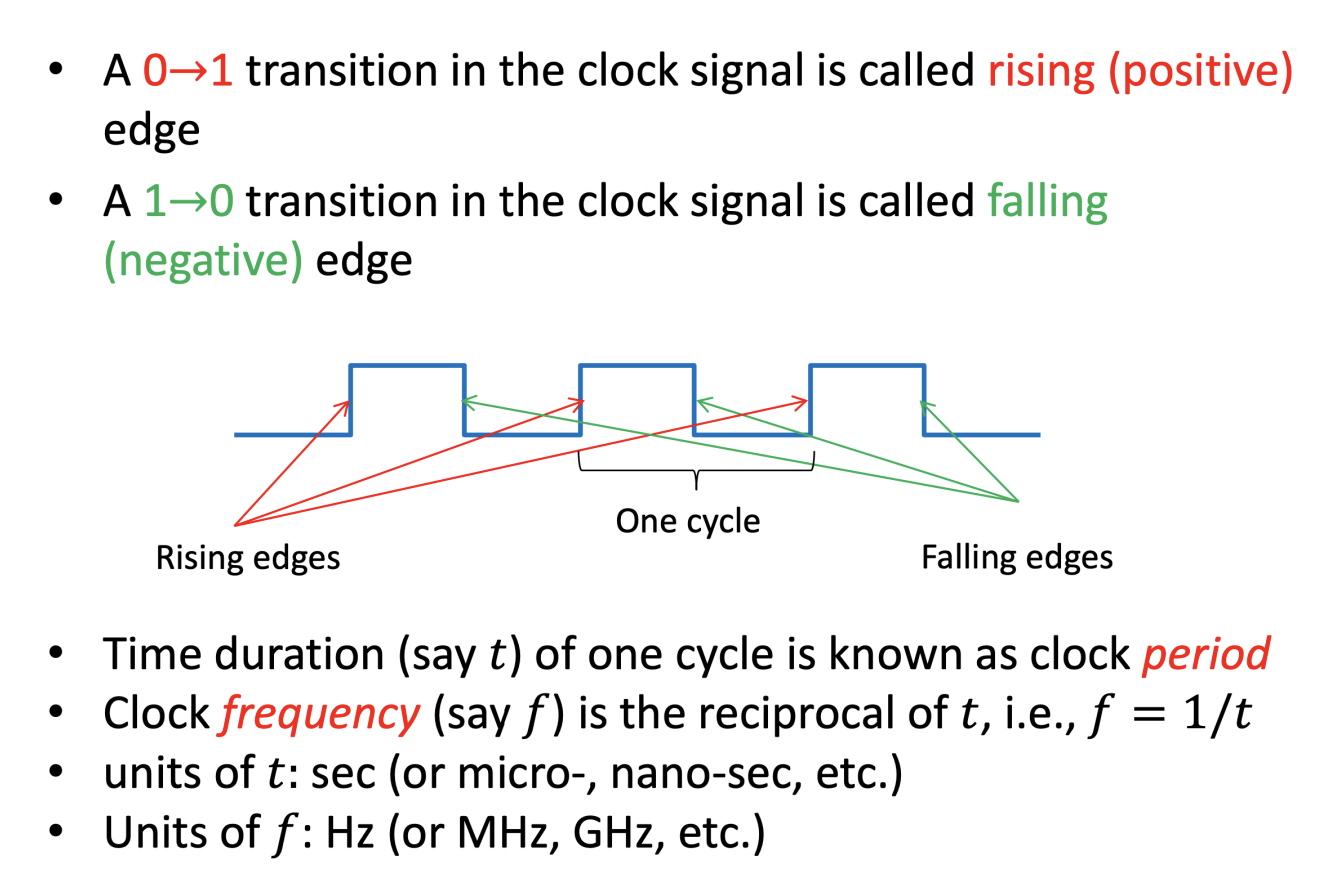

Rising Edge and Falling Edge

Triggering Methods

1. Level Triggering (Latch)

- When Clock is high, there is transition.

2. Edge Triggering (Flip-Flop)

- Positive edge triggering (L→H)

- Negative-edge triggering (H→L)

- We can get edge triggering using a Differentiator Circuit

How do clocks work from a hardware perspective?

How can they provide such a consistent signal?

- When you press down a button, you might actually trigger multiple presses instead of a single one. This is where you need a