Translation-Lookaside Buffer (TLB)

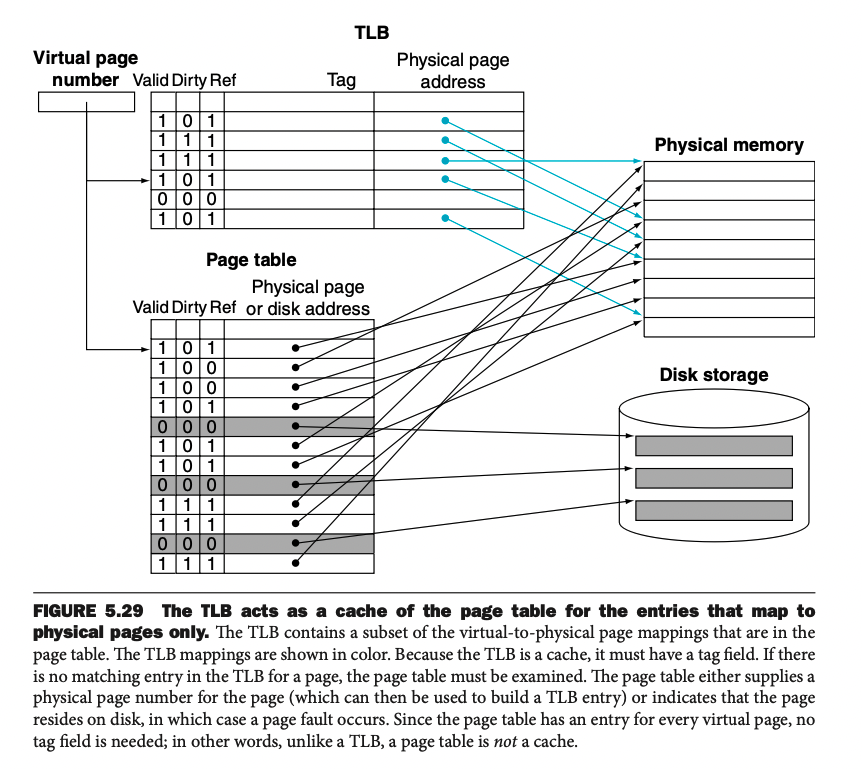

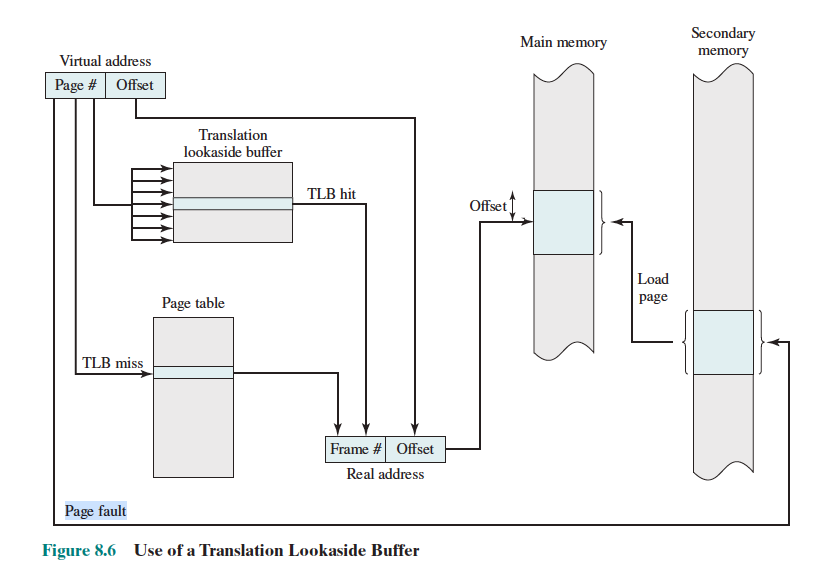

Translation-lookaside buffer (TLB) is a Cache that keeps track of recently used address mappings to try to avoid an access to the page table.

- It’s used to make address translation fast

Why TLBs?

In principle, every virtual memory reference can cause two physical memory accesses: one to fetch the appropriate page table entry, and another to fetch the desired data. This would be very slow.

To overcome this problem, most virtual memory schemes make use of a special high-speed cache for page table entries called a TLB.

- The TLB makes address translation fast

This should be called a translation cache.

Is the cache mostly about TLB then?

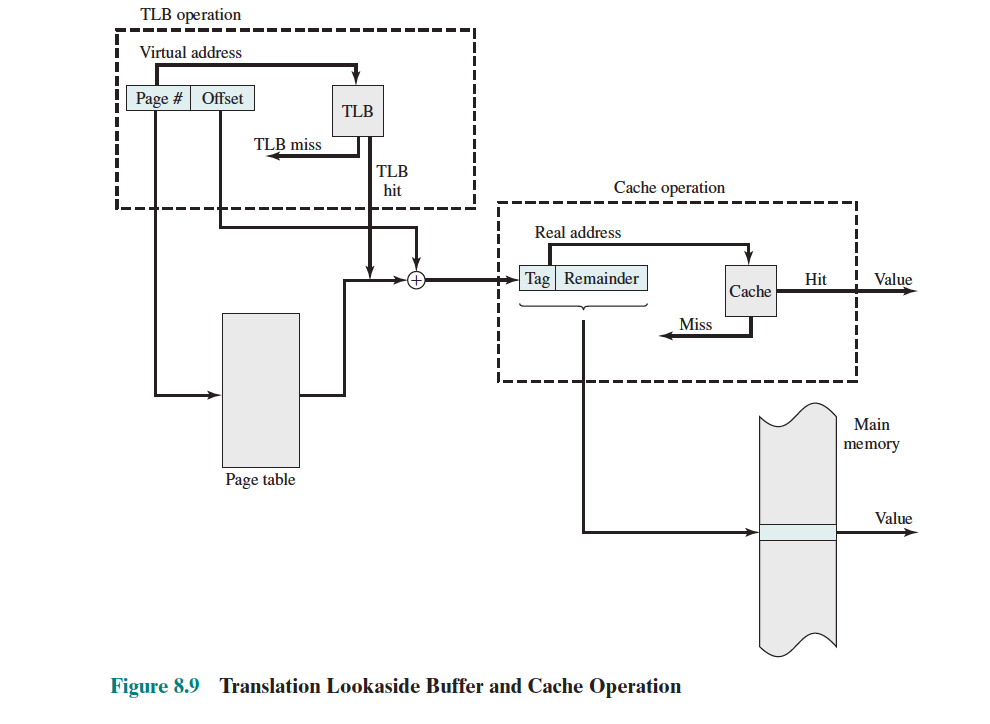

No, separate from the TLB, there are caches dedicated to storing data and instructions. TLB simply tells you the mapping from virtual to physical address. L1 / L2 cache lets you retrieve that data really fast since it is already cached.

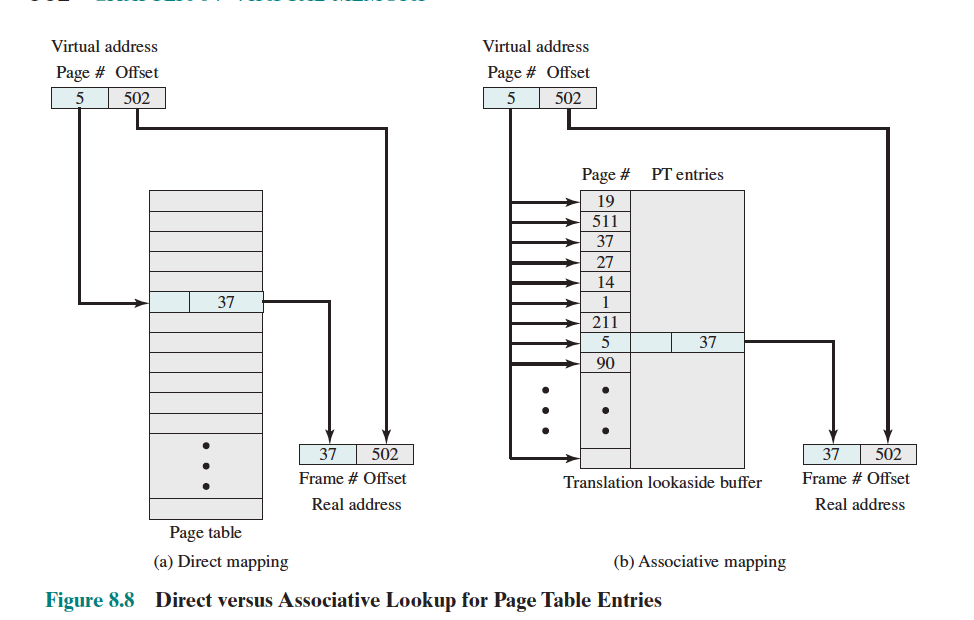

So basically, you use the VPN as a tag into the TLB. If the TLB is full, then you just remove the oldest one. Else, you add it to the TLB.

- That way, instead of looking at the physical memory, and accessing the data from there (especially if you think about the Multi-Level Page Table which can start getting slow), you have this sort of Cache that takes care of it.

See video: https://www.youtube.com/watch?v=DkxqhOZ1OYo&ab_channel=MatthewWatkins

MOST HELPFUL Diagram

In terms of how the TLB is actually implemented under the hood, it’s very similar to caching. See Direct Mapped Cache and Set Associative Cache.

This is a similar diagram from ECE222