Datapath

A datapath is the component of the processor that performs arithmetic operations.

- Composed of Datapath elements

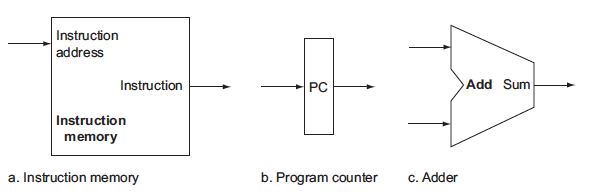

Datapath Element: A unit used to operate on or hold data within a processor. As we will see below, in RISC-V, these are

- Instruction Memory

- Program Counter

- Adder

- Register File

- ALU

- Data Memory

- Immediate Generation Unit

4.3 Building a Datapath

Part 1: Fetching instructions and incrementing the program counter We need 3 things (2 State Element + 1 Adder)

- Instruction Memory

- A Memory unit that stores the instructions of a program and supply instructions given an address

- reflects the contents of the location specified by the address input

- Program Counter (PC)

- 32-bit register that is written at the end of every clock cycle

- Adder (an ALU)

- Increments the PC to the address of the next instruction

- Adds two 32-bit inputs and place the sum on its output

Part 2: Running the Instructions As we talked about before in RISC-V Implementation, different types of instructions run differently:

- Arithmetic-logical instructions (R-Type Instructions) (

add,sub,and,or) - Memory Reference (

sw,lw) - Branches (Conditional branch instruction

beq)

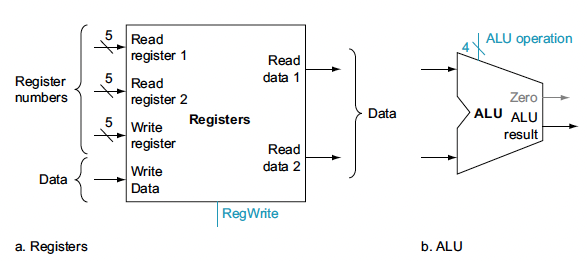

R-Format Instructions

These instructions read two registers, perform ALU operation, and writes the result to a register. It’s very simple, you need two elements

- Register File to read the contents of the registers

- ALU to perform the ALU operation

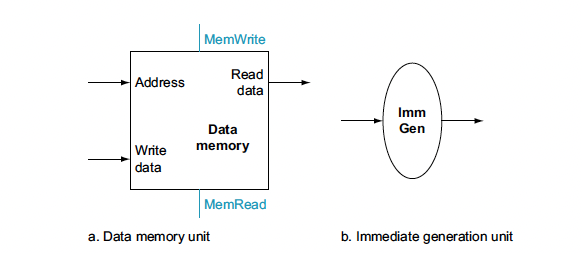

Load and stores Instructions

ex: lw x1, offset(x2) or sw x1, offset(x2). These instructions compute a memory address by adding the base register to the 12-bit signed offset field contained in the instruction.

In addition to Register File and ALU, we also need other datapath units.

We need to Sign-Extend the 12-bit field into a 32-bit signed value.

To read from or write to memory, we use a Data Memory Unit (see image below).

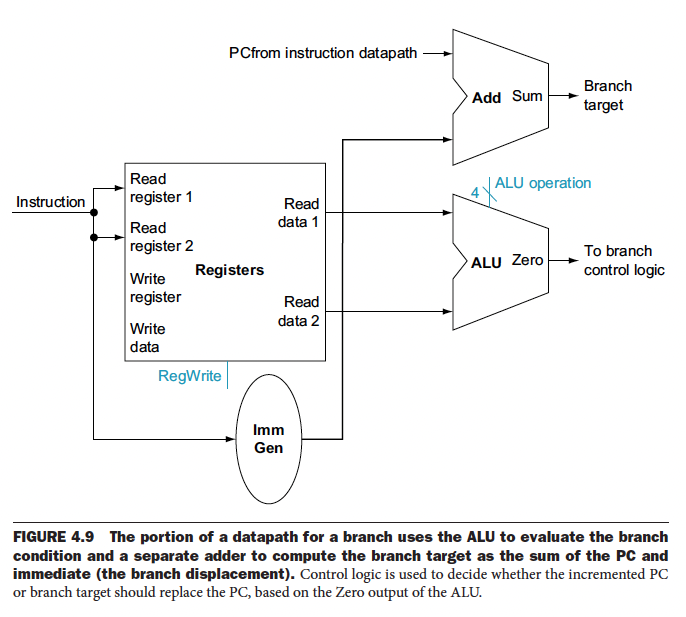

BEQ instruction beq

ex: beq, x1, x2, offset. The 12-bit offset is used to compute the branch target address relative to the branch instruction address.

To compute our branch target address, we use

- Immediate Generation Unit (ImmGen)

- has a 32-bit instruction as input that selects a 12-bit field for load, store, and branch if equal that is sign-extended into a 32-bit result appearing on the output (see Chapter 2)

- has a 32-bit instruction as input that selects a 12-bit field for load, store, and branch if equal that is sign-extended into a 32-bit result appearing on the output (see Chapter 2)

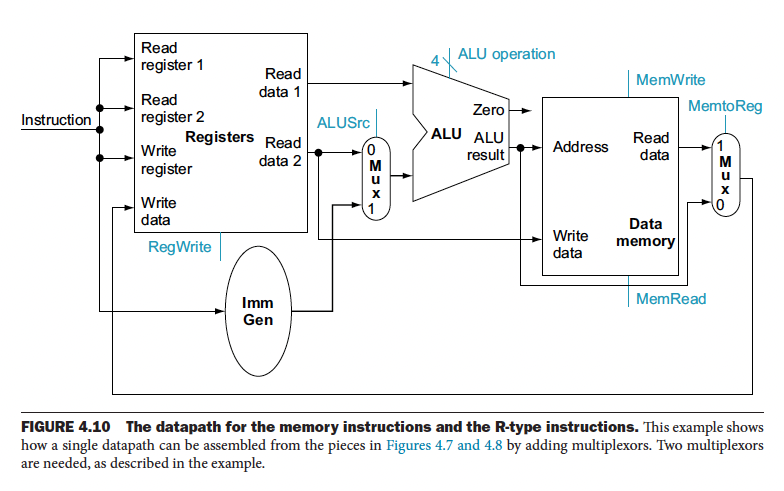

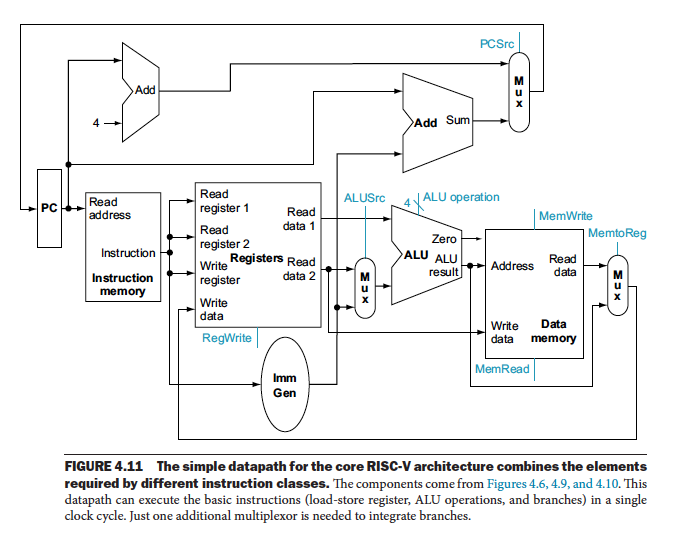

Everything together

This would be the Datapath for both R-Type Instructions and the memory instructions.

This would be the Datapath for handling beq (branching) instruction.

Combining all three types of instructions, you have the following Datapath.

Next

The texts in blue represent control lines. We need to design a Control Unit to control these.

We also want to look at a multi-cycle implementation.